Monolithic three-dimensional integration with 2D material-based p-type transistors

- 저자

- Taoyu Zou* , Youjin Reo, Seongmin Heo, Haksoon Jung, Soonhyo Kim, Ao Liu*, Yong-Young Noh*

- 저널명

- Materials Science and Engineering, 163, 100893 (2025)

- 년도

- 2025

[Abstract]

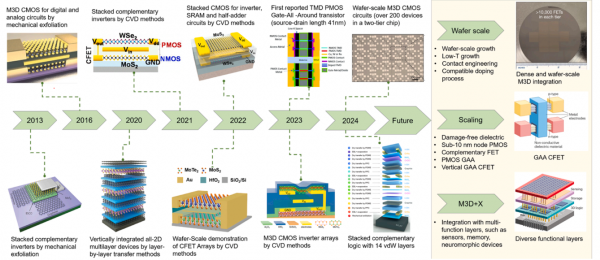

Monolithic three-dimensional (M3D) integration offers a promising solution to the limitations of silicon (Si) integrated circuits as they reach their physical limits, including problems with power use and heat dissipation. By enabling the vertical stacking of multiple device layers, M3D integration significantly increases device density, enhances performance, and reduces power consumption and communication delays between components. Twodimensional (2D) materials, recognized for their exceptional electrical properties and minimal thickness, offer a promising approach to advancing the scaling of complementary metal-oxide-semiconductor (CMOS) transistors. 2D material-based p-type transistors play a vital role in creating CMOS circuits with low static power dissipation and high noise immunity, which are critical for the efficiency and reliability of electronic devices. Although significant progress has been made in developing n-type 2D transistors and integrating them into M3D architectures, advancements in M3D integration with p-type 2D transistors are still in the early stages. Here, the recent status and ongoing challenges in M3D integration are reviewed, focusing on 2D materials-based p-type transistors. We provide an overview of key 2D p-type materials and their synthesis techniques, followed by a detailed discussion of integration strategies, including planar integration, 3D stacked complementary transistors, and M3D integration. Finally, we discuss the challenges, potential strategies, and opportunities in achieving M3D integration with high-performance 2D p-type transistors. The review aims to provide a foundational understanding for driving future innovations in high-performance, energy-efficient, and densely integrated M3D CMOS electronic devices.