Contact Engineering with Selenium Interlayers for High-Performance p-Type Two-Dimensional WSe2 Transistors

- 저자

- Soonhyo Kim, Seongmin Heo, Mingyu Kim, Youjin Reo, Inseob Shin, Gwon Byeon, Yong-Sung Kim*, Taoyu Zou*, Yong-Young Noh*

- 저널명

- Advanced Functional Materials (2026) e27684

- 년도

- 2026

- Link

- https://doi.org/10.1002/adfm.202527684 53회 연결

[Abstract]

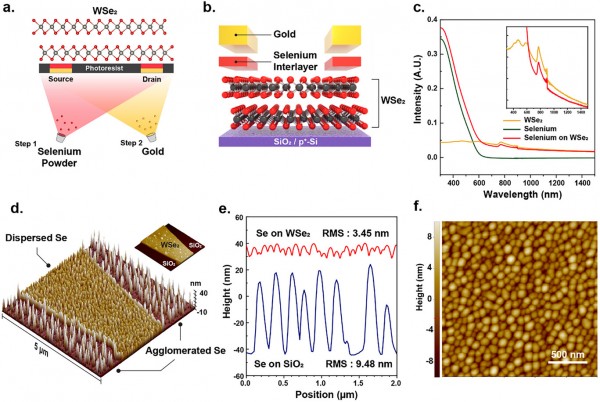

The development of high-performance p-type 2D transistors is hindered by Fermi level pinning (FLP) caused by the direct deposition of the contact metal on the 2D semiconducting layer, resulting in a Schottky barrier that limits efficient hole injection. In this study, we demonstrate a contact engineering strategy that enhances the p-type 2D transistor performance by inserting a selenium interlayer (SIL) between the contact metal and transition metal dichalcogenide (TMD). Utilizing the physics of Fermi level pinning, we optimize the Fermi level to deeper levels at the metal-selenium interface, enhancing hole injection. Through SIL insertion, the average hole field-effect mobility of WSe2 transistors increases significantly from 23 to 107 cm2 V−1 s−1, and the on-current density from 8.4 to 55 µA/µm. The on/off current ratio exceeds 108, and the maximum mobility reaches 119 cm2 V−1 s−1. The effectiveness of this approach is demonstrated in various p-type TMD channels, including WSe2, WS2, and MoSe2, as well as in various metal electrodes, all of which exhibit enhanced hole injection. This work provides a simple method to enhance the performance of p-type 2D transistors by improving the hole injection efficiency.