Hysteresis-Free Solution-Processed 2-D MoS2 Flake-Thin-Film Transistors With Improved Operational Stability

- 저자

- Taoyu Zou, Seongmin Heo, Ao Liu, Gwon Byeon, Huihui Zhu*, Yong-Young Noh*

- 저널명

- IEEE Transactions on Electron Devices, 70, 9, 4680-4684 (2023)

- 년도

- 2023

- Link

- https://doi.org/10.1109/TED.2023.3298313 539회 연결

[Abstract]

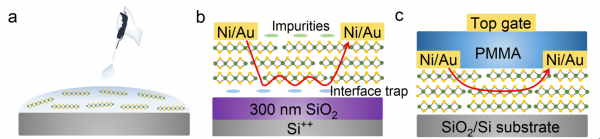

An interface trap negatively affects the performance of a thin-film transistor (TFT). In the current study, we demonstrate hysteresis-free solution-processed MoS2 TFTs with a significantly reduced trap density of 3.7 × 1010 cm−2 using a poly(methylmethacrylate) (PMMA) dielectric in a top-gate top-contact (TGTC) device structure, which is much lower than that with a SiO2 back-gate dielectric layer (7.9 × 1011 cm−2 ). The TFTs show a field-effect mobility of 7 cm2 /V s for both forward and reverse scans, with an ON/OFF current ratio of >106 . In addition, after 3000 s of the bias-stress test, the drain current of the device degrades by only 7%.